时间:2017-08-28 10:36

人气:

作者:admin

近日,在加州Hot Chips大会上,百度发布了XPU,这是一款256核、基于FPGA的云计算加速芯片,合作伙伴是赛思灵(Xilinx)。百度也在这次的大会上,透露了关于这款芯片的更多架构方面的细节。

过去几年,百度在深度学习领域,尤其是基于GPU的深度学习领域取得了不错的进展。而且,百度也在开发被称作XPU的新处理器。

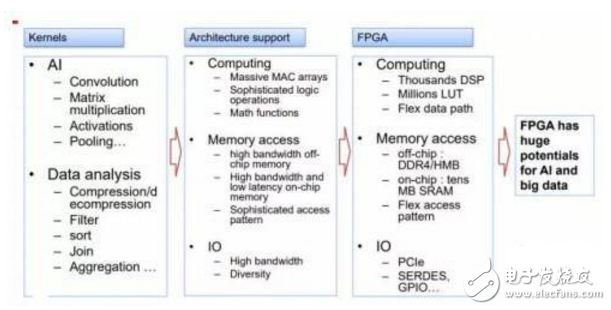

百度解释了FPGA上AI和数据分析工作负载的情况

百度研究员欧阳剑表示,百度设计的芯片架构突出多样性,着重于计算密集型、基于规则的任务,同时确保效率、性能和灵活性的最大化。今天,他在Hot Chips大会上与来自FPGA厂商Xilinx的人士一同发布了XPU。

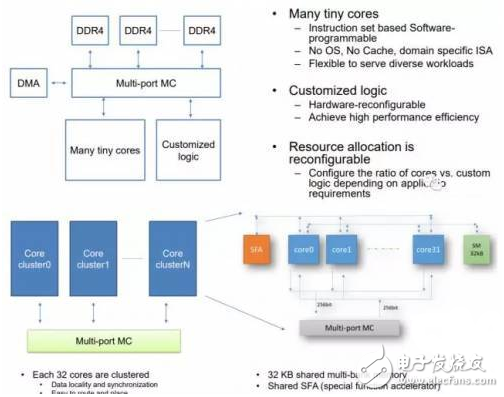

XPU的目标是在性能和效率之间实现平衡,并处理多样化的计算任务。FPGA加速器本身很擅长处理某些计算任务,但随着许多小内核交织在一起,多样性程度将会上升。

欧阳剑表示:“FPGA是高效的,可以专注于特定计算任务,但缺乏可编程能力。传统CPU擅长通用计算任务,尤其是基于规则的计算任务,同时非常灵活。GPU瞄准了并行计算,因此有很强大的性能。XPU则关注计算密集型、基于规则的多样化计算任务,希望提高效率和性能,并带来类似CPU的灵活性。”

目前XPU有所欠缺的仍是可编程能力,而这也是涉及FPGA时普遍存在的问题。到目前为止,XPU尚未提供编译器。不过欧阳剑表示,该团队将会很快开发一款编译器。

欧阳剑还表示为了支持矩阵、卷积,以及其他大大小小的内核,我们需要一个配备高带宽低延时内存,以及高带宽I/O接口的大型数学阵列。FPGA中XPU的DSP单元提供了并行处理能力,片外DDR4和HBM接口优化了数据传输,而片上SRAM则提供了必要的存储特性。

在Micro Benchmark测试中,对于计算密集型、常规内存访问的计算任务,XPU的效率与x86内核类似。对于数据同步的计算任务,XPU的可扩展性应当可以进一步优化。而对于没有数据同步的计算任务,XPU的可扩展性与核心数量呈线性关系。

这就是问题所在。如前所述,XPU仍然没有配备编译器。这款处理器在FPGA上实现,通过订制的逻辑电路提供指令。这些小核心类似于CPU,开发者只能使用汇编语言,而所有的执行都由主机来控制。整个流程包括拆分计算任务,编写XPU代码,调用专用的逻辑函数,从而在Linux平台上进行编译和运行。

XPU具有256个内核,集成了一个共享内存用于数据同步,所有内核都运行在600MHz。

欧阳剑称:“在百度,我们使用FPGA已有多年时间。我们的数据中心、云计算平台和自动驾驶项目中有大量FPGA。我们非常了解FPGA的优缺点,以及如何优化。凭借XPU的大型核心,我们专注于多样化的计算任务。”

去年有媒体报道了基于百度深度学习SDA的SQL加速器。当时的数据流基于SA架构。根据欧阳剑的描述,这也是XPU内存带宽和延时优势的核心。

欧阳剑同时展示了今年完成的一些benchmark测试,但信息非常粗略。不过,这只是百度第一次公开展示XPU。

如果XPU被证明可以用于AI、数据分析、云计算和无人驾驶,那么百度可能需要用ASIC技术去开发XPU